#### Mercoledì 2 Aprile 2014

#### OUTLINE

- Mobile Traffic outlook

- Trend in HW development of telecom and datacom equipments

- Silicon Photonics and the related technological issues

- Silicon Photonics Applications in interconnect

- Silicon Photonics applications in optical networking

- Longer term research on Graphene

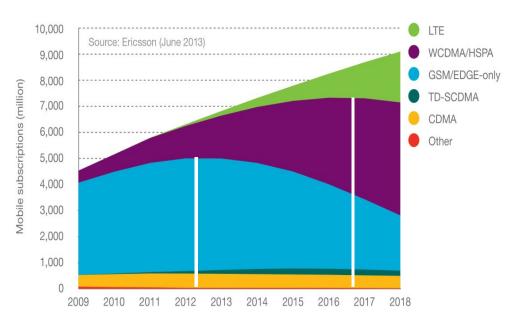

## 9.1 BILLION MOBILE SUBSCRIPTIONS END 2018

#### New subscriptions added in Q1 2013

- LTE is now growing strongly, with 20 million new subscribers

- WCDMA/HSPA around 60 million, i.e. 3X more than LTE

- GSM/EDGE-only added around 30 million

- LTE reached 100 million subscriptions in beginning of June 2013

- LTE to reach 2 billion subscriptions by 2018

#### Mobile subscriptions by technology, 2009-2018

M2M subscriptions not included

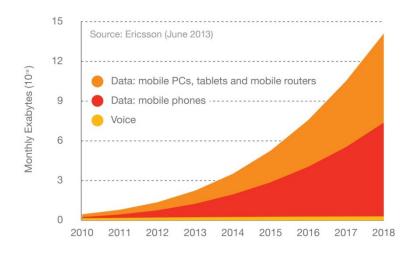

## 12 TIMES MOBILE DATA TRAFFIC BY END OF 2018

Monthly consumption per device type

2012

2018

2.5 GB

0.6 GB

3.1 GE

0.45 GB

2 GB

Global mobile traffic: voice and data 2010-2018

## CURRENT TREND IN HW PLATFORMS OF TELECOM | AND DATACOM EQUIPMENTS

Due to the gap between traffic demand explosion and bandwidth supply capability (Moore's law) there is a strong focus on reducing:

- Cost

- Power consumption

- Footprint

- Architectural simplifications

Electronic ASICs continue to scale following Moore's but chip-to-chip, board-to-board and rack-to-rack interconnection has become a bottleneck

Simplifying system architecture by leveraging on novel photonic devices and photonic integration for interconnections and optical off-loading in routers and switches.

Key photonic integrated devices (under development as proprietary components) will become the strong differentiating factor for future platforms.

#### WHY SILICON PHOTONICS

Among the different technologies to integrate on the same chip many optical functions (detectors, lasers, modulators, mux/demux etc) Silicon Photonics is considered the most promising technology for:

- cost advantage due to the use of well developed CMOS infrastructure and high yield if produced in volume

- the smallest footprint due to the use of high refractive index contrast that allows to implement waveguides in nano-scale dimensions

- the high efficiency in energy consumption due to the possibility to integrate the photonic circuits with the related electronic driving circuits or ASICs

But Si Ph presents also some technological issues to be solved for a full exploitation of its potential

### HOT TOPICS IN SILICON PHOTONICS DEVELOPMENT

#### >Co-Integration of photonic circuits and electronic circuits in Silicon

To find the most effective technique for integrating effectively both electronic and photonic circuits on the same device:

- > monolithic integration?

- > wafer-wafer bonding?

- > Cu-pillar for die-to-die interconnections?

#### > Hybrid bonding of III-V blocks on silicon-on-insulator substrates

To find the most effective technique to integrate optical functions that have necessarily be implemented in III-V material with Silicon substrates (lasers and in most cases modulators and photodiodes):

- > co-package mounting?

- > evanescent coupling?

- > Other alignment-free bonding technique at wafer level

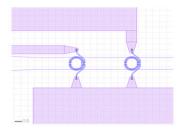

#### Fiber coupling to silicon chip:

To find the most effective technique for low cost, low loss, wide band, small area and low profile fiber coupling scheme including multiple fiber coupling. This considering also the possibility to perform optical tests of the chips at wafer level:

- > grating couplers?

- > spot size converters?

# DATA CENTERS: THE FIRST APPLICATION OF SILICON PHOTONICS

Bottleneck at servers electrical interconnection via 1 GE cables Replacement with 10G optical interconnect based on conventional optics has too low density, too high cost and too high power consumption

Silicon Photonics 40 interconnect by Luxtera

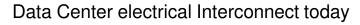

## HIERARCHICAL DATA CENTER NETWORK ARCHITECTURE AND ITS TRANSFORMATION

#### **New Trend:**

- Hierarchical simplification

- Increased rate of interconnect

- Replacement of copper cables with fiber cables

network

Innovazione e ricerca

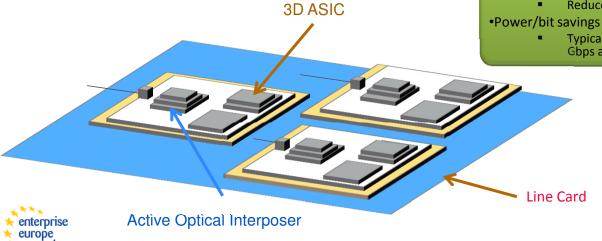

### OPTICAL FOR 2.5D/3D ASICS

#### OPTICAL INTERPOSERS FOR HIGH INTERCONNECT BANDWIDTH AND DENSITY

Novel architectures enabled by key photonic technologies for future Radio **Base Station and Routers**

#### Drivers for 2.5D/3D optical ASICS

- •Less real estate

- Bulky and power hungry connectors (SFP) blocking air inlets

- High Bandwidth Density

- >5 Tb/s/cm2 achievable

- Board complexity reduction

- Especially for 25 Gb/s and beyond

- Reduced cost of material; move from MG6 to FR4 possible

- - Typically 8-10 pJ/bit (compared to 20-40 pJ/bit for copper) @ 10 Gbps and decreasing by 50% every 3 year

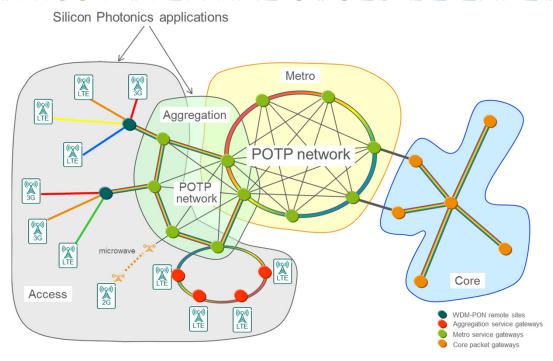

## OPTICAL TRANSPORT NETWORK: WHERE SILICON PHOTONICS POTENTIAL COULD BE EXPLOITED

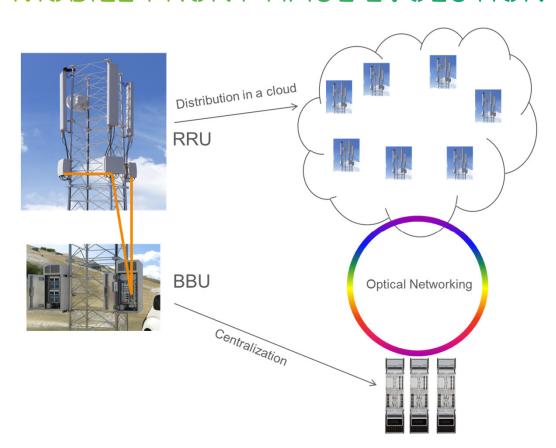

## MOBILE FRONT-HAUL EVOLUTION

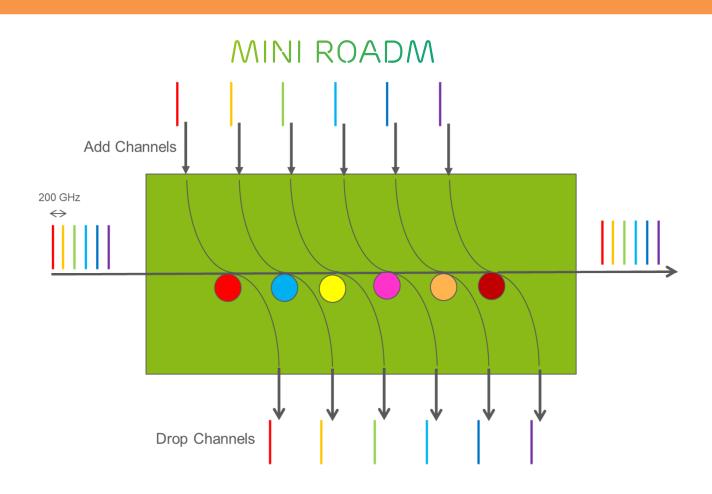

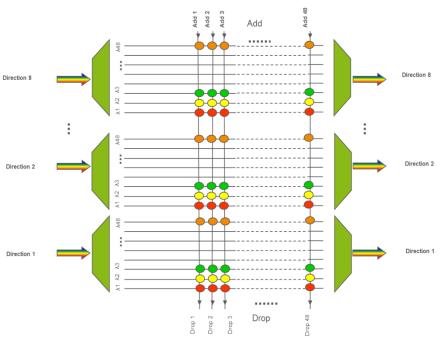

## MINI ROADM

The Mini-ROADM allows introducing optical switching in access networks, mobile backhaul, and data centers where high volume and low cost are required.

The Mini-ROADM also adds flexibility to ROADM in metro networks, at low cost.

Opportunities are the reduction of the switch cost of more than one order of magnitude respect to current technologies and the reduction of the switch footprint from a box to a chip.

Challenges are the complexity of wavelength control, the performances in terms of crosstalk, loss, bandwidth and the integration of many different photonic processing functions.

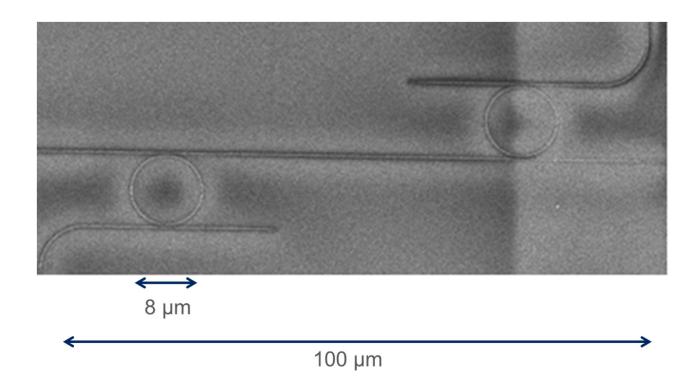

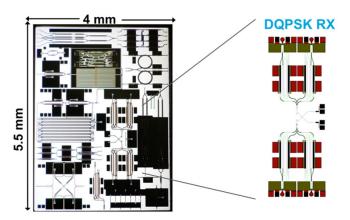

The use of the Multi Project Wafer (MPW) shuttles it's the way to realize our own prototypes at an affordable cost and with the real guarantee of the CMOS compatibility.

## SEM PHOTO OF THE SWITCH ELEMENT

## TRANSPONDER AGGREGATION

IRIS PROJECT FP7-STREP 619194

Time frame: 2014-2016

Partners:

**Ericsson**

ST

**CEA-LETI**

**CNIT**

Univ. Wien

Univ. Valencia

Univ. Trento

**ETRI**

1000+ functions integrated in one chip!

## WHAT'S COOKING IN TUSCANY

Silicon Photonic Design Center setup at S.Anna University - CNIT for the development of Opto IC, including packaging facilities

Mini ROADM

Chip realization

## **BEYOND THE LIMITS: GRAPHENE**

- One atomic layer (0.34 nm)

- Quantum confinement by nano ribbons or nano tubes

- Low losses (0.13 dB/μm)

- ~100 GHz Intensity modulation speed

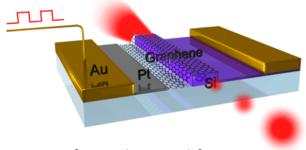

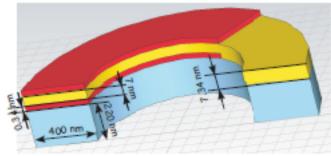

#### Waveguide Intensity Modulator

[Xiang Zhang et Alii]

[M. Romagnoli et Alii]

#### **ERICSSON INTEREST IN GRAPHENE**

- > Ericsson is active in the research of silicon photonic devices

- To achieve practical active optical components on silicon photonics, the integration of materials such as Ge or III-V compounds has been implemented until today, which significantly increased cost

- Graphene and related materials have the potential to improve the energy efficiency to < 0.5 pJ/bit, while they can be implemented by low-cost conventional semiconductor processes</p>

- Graphene can therefore help to overcome the main optical interconnect challenges of cost and energy efficiency and make optical inter-connects the technology of choice for chip-to-chip and eventually on-chip interconnects

#### CONCLUSIONS

- Silicon photonics and its applications are in line with the current trends in Telecom and Datacom applications

- The aim of introducing the silicon photonic approach in the future evolution

of its own system is to enable flexible telecommunication networks with fast

response and capable to handle huge amount of traffic and with an

increased number of functionalities in a single telecommunication system

- To go beyond the limit of Si Ph, Ericsson is evaluating Graphene potential for longer term applications